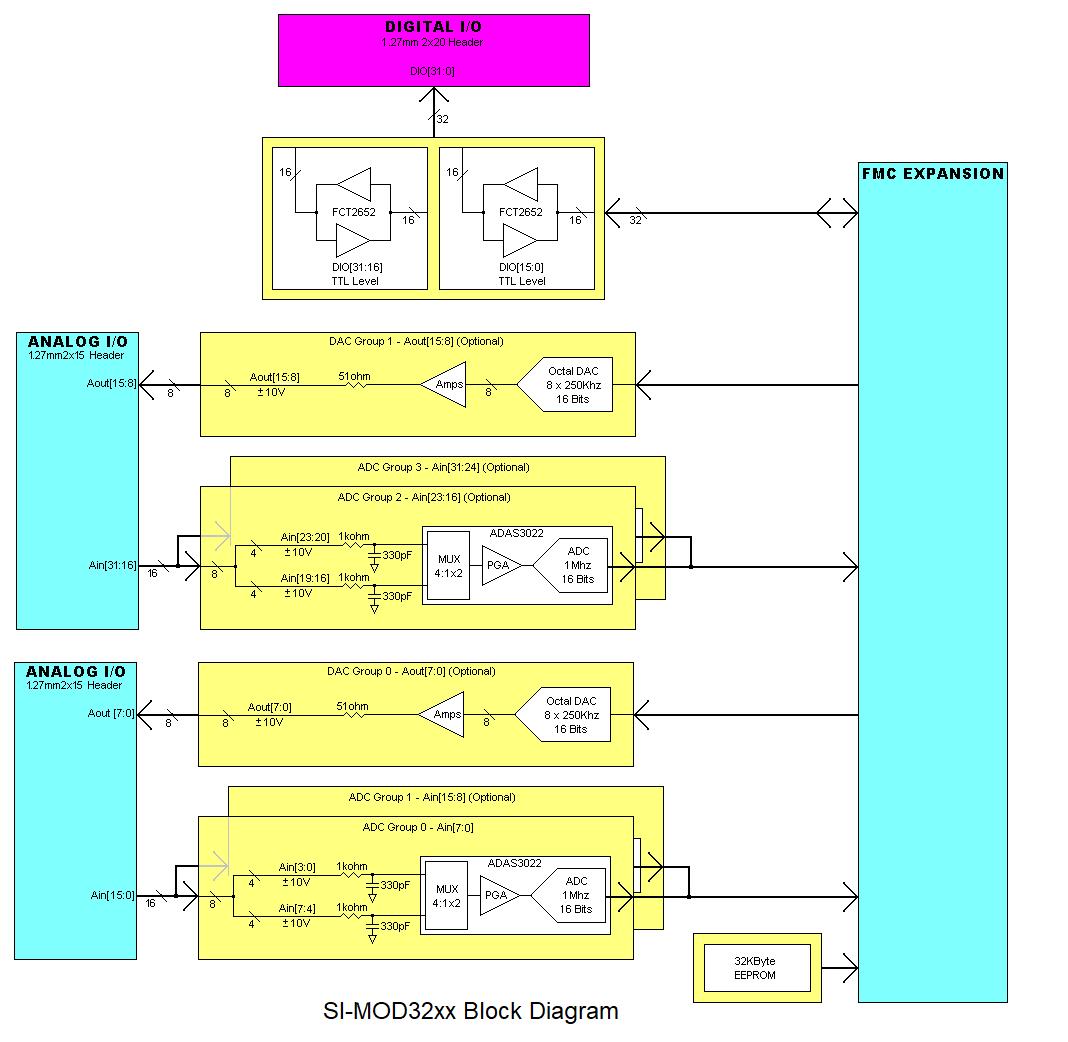

The FPGA controls up to four (4) ADAS3022, 16 bit, 8 channel 1Mhz additive sampling ADC devices, for up to a maximum of 32 input channels with bipolar inputs that ranges between ±10V (20Vpp).

The only ancillary front end circuit includes a passive, single pole low pass RC filter with Fc = 482.3khz for each input.

The following ADAS3022 pins are tied to the FMC connector and are controlled by the carrier's FPGA with +2.5Vdc~+3.3Vdc compatibility:

| ADAS3022 Pins Tied to FMC Connector | |

| Signal Name | Description |

| ADC_RST | HI asserted universal reset command common to all 4 ADCs |

| ADC_SCLK | Universal 25Mhz~34Mhz SPI clock signal common to all 4 ADCs |

| ADCn_SDIN | SPI data input for ADCn, n=3:0 |

| ADCn_SDOUT | SPI data output from ADCn, n=3:0 |

| ADCn_CSn | LO asserted SPI chip select for ADCn, n=3:0 |

| ADCn_CNVRT | LO->HI edge convert command for ADCn, n=3:0 |

| ADCn_BUSY | HI asserted busy indicator, HI->LO edge indicates conversion is complete, n=3:0 |

The FPGA controls up to two (2) LTC2666, 16 bit, 8 channel 250khz additive updating DAC devices, for up to a maximum of 16 output channels. Each DAC output channel is buffered with a voltage opamp.

The LTC2666 is configured by default to operate in bipolar mode with outputs that range ±10V (20Vpp) where the configuration pins MSP[2:0] = LO. However, please consult the factory to change the default operating mode to one of the various available unipolar or bipolar modes, or a mode where the ranges are set in software.

The following LTC2666 pins are tied to the FMC connector and are controlled by the carrier's FPGA with +2.5Vdc~+3.3Vdc compatibility:

| LTC2666 Pins Tied to FMC Connector | |

| Signal Name | Description |

| DAC_CLRn | LO asserted universal clear/reset command common to both DACs |

| DACn_SCLK | 50Mhz SPI clock signal for DACn, n=3:0 |

| DACn_SDI | SPI data input for DACn, n=3:0 |

| DACn_SDO | SPI data output from DACn, n=3:0 |

| DACn_CSn | LO asserted SPI chip select for DACn, n=3:0 |

| DACn_LDAC | LO asserted load command for DACn, n=3:0 |

| DACn_TGP | Asynchronous edge based toggle command to update internal registers for DACn, n=3:0 |

The FPGA controls four (4) 74FCT2652 8 bit transceivers, with two (2) devices making up each 16 bit bidirectional buffered port, for a maximum thirty two (32) lines, with +3.3Vdc~+5Vdc tolerance on the IO lines. When a port is configured as an input, it operates as a non-registered transceiver. Meanwhile as an output, it operates as a registered transceiver.

A pair of generic 30 pin, 0.050" pitch (1.27mm) connectors are used to interface the external analog I/O signals. Below is the connection diagram:

| P2: First 30 Pin Connector | |||||||

| Circuit | SE Signal/DE | 30 Pins | SE Signal/DE | ||||

| ADC0 (Channels[7:0]) | IN0/IN0+ | 1 | 2 | IN1/IN0- | |||

| IN2/IN1+ | 3 | 4 | IN3/IN1- | ||||

| IN_COMMON0 | 5 | 6 | IN4/IN2+ | ||||

| IN5/IN2- | 7 | 8 | IN6/IN3+ | ||||

| IN7/IN3- | 9 | 10 | AGND | ||||

| ADC1 (Channels[15:8]) | IN8/IN4+ | 11 | 12 | IN9/IN4- | |||

| IN10/IN5+ | 13 | 14 | IN11/IN5- | ||||

| IN_COMMON1 | 15 | 16 | IN12/IN6+ | ||||

| IN13/IN6- | 17 | 18 | IN14/IN7+ | ||||

| IN15/IN7- | 19 | 20 | AGND | ||||

| DAC0 (Channels[7:0]) | OUT0 | 21 | 22 | OUT1 | |||

| OUT2 | 23 | 24 | OUT3 | ||||

| AGND | 25 | 26 | OUT4 | ||||

| OUT5 | 27 | 28 | OUT6 | ||||

| OUT7 | 29 | 30 | AGND | ||||

| P3: Second 30 Pin Connector | |||||||

| Circuit | SE Signal/DE | 30 Pins | SE Signal/DE | ||||

| ADC2 (Channels[23:16]) | IN16/IN8+ | 1 | 2 | IN17/IN8- | |||

| IN18/IN9+ | 3 | 4 | IN19/IN9- | ||||

| IN_COMMON2 | 5 | 6 | IN20/IN10+ | ||||

| IN21/IN10- | 7 | 8 | IN22/IN11+ | ||||

| IN23/IN11- | 9 | 10 | AGND | ||||

| ADC3 (Channels[31:24]) | IN24/IN12+ | 11 | 12 | IN25/IN12- | |||

| IN26/IN13+ | 13 | 14 | IN27/IN13- | ||||

| IN_COMMON3 | 15 | 16 | IN28/IN14+ | ||||

| IN29/IN14- | 17 | 18 | IN30/IN15+ | ||||

| IN31/IN15- | 19 | 20 | AGND | ||||

| DAC1 (Channels[15:8]) | OUT8 | 21 | 22 | OUT9 | |||

| OUT10 | 23 | 24 | OUT11 | ||||

| AGND | 25 | 26 | OUT12 | ||||

| OUT13 | 27 | 28 | OUT14 | ||||

| OUT15 | 29 | 30 | AGND | ||||

Below is a chart of the four (4) ADC and two (2) DAC interconnections between the FMC connector's LPC columns, and the Altera Cyclone 5GX FPGA device:

| ADCs, FMC & FPGA Connections | ||||

| Section | Signal | FMC Connector Pin | FPGA Bank & Pin | Direction |

| ADC[3:0] Control | ADC_RST | G24 | Bank 7A-B12 | FPGA->ADC[3:0] |

| ADC_SCLK | H16 | Bank 7A-B15 | ||

| ADC0-Channels[7:0] | ADC0_CNVRT | D17 | Bank 7A-E10 | FPGA->ADC0 |

| ADC0_CSn | G16 | Bank 7A-H13 | ||

| ADC0_SDIN | H17 | Bank 7A-C15 | ||

| ADC0_SDOUT | G15 | Bank 7A-H14 | ADC0->FPGA | |

| ADC0_BUSY | D18 | Bank 7A-E11 | ||

| ADC1-Channels[15:8] | ADC1_CNVRT | H20 | Bank 8A-E9 | FPGA->ADC1 |

| ADC1_CSn | H19 | Bank 8A-D8 | ||

| ADC1_SDIN | C18 | Bank 7A-A23 | ||

| ADC1_SDOUT | C19 | Bank 7A-A22 | ADC1->FPGA | |

| ADC1_BUSY | G18 | Bank 7A-H18 | ||

| ADC2-Channels[23:16] | ADC2_CNVRT | C22 | Bank 7A-B21 | FPGA->ADC2 |

| ADC2_CSn | D21 | Bank 7A-A21 | ||

| ADC2_SDIN | G19 | Bank 7A-H17 | ||

| ADC2_SDOUT | D20 | Bank 7A-B22 | ADC2->FPGA | |

| ADC2_BUSY | C23 | Bank 7A-B20 | ||

| ADC3-Channels[31:24] | ADC3_CNVRT | G22 | Bank 8A-E6 | FPGA->ADC3 |

| ADC3_CSn | G21 | Bank 8A-D6 | ||

| ADC3_SDIN | H22 | Bank 7A-A14 | ||

| ADC3_SDOUT | H23 | Bank 7A-B14 | ADC3->FPGA | |

| ADC3_BUSY | H25 | Bank 7A-A8 | ||

| DAC[1:0] Control | DAC_CLRn | H10 | Bank 5A-V22 | FPGA->DAC[1:0] |

| DAC0-Channels[7:0] | DAC0_TGP | H14 | Bank 7A-D16 | FPGA->DAC0 |

| DAC0_LDACn | G12 | Bank 7A-E20 | ||

| DAC0_CSn | G13 | Bank 7A-E19 | ||

| DAC0_SCLK | C14 | Bank 7A-B24 | ||

| DAC0_SDI | D15 | Bank 7A-D20 | ||

| DAC0_SDO | D14 | Bank 7A-D21 | DAC0->FPGA | |

| DAC1-Channels[15:8] | DAC1_TGP | H11 | Bank 5A-U22 | FPGA->DAC1 |

| DAC1_LDACn | D11 | Bank 7A-E18 | ||

| DAC1_CSn | D12 | Bank 7A-F18 | ||

| DAC1_SCLK | H13 | Bank 7A-E16 | ||

| DAC1_SDI | C11 | Bank 7A-M12 | ||

| DAC1_SDO | C10 | Bank 7A-N12 | DAC1->FPGA | |

NOTES:

A generic 40 pin, 0.050" pitch (1.27mm) connector is used to interface the external digital I/O signals. Below is the connection diagram:

| P4: SI-MOD32xx 40 Pin Connector | |||

| Signal | 40 Pins | Signal | |

| DGND | 1 | 2 | DIO0 |

| DIO1 | 3 | 4 | DIO2 |

| DIO3 | 5 | 6 | DIO4 |

| DIO5 | 7 | 8 | DIO6 |

| DIO7 | 9 | 10 | DIO8 |

| DIO9 | 11 | 12 | DIO10 |

| DIO11 | 13 | 14 | DIO12 |

| DIO13 | 15 | 16 | DIO14 |

| DIO15 | 17 | 18 | DGND |

| DIO17 | 19 | 20 | DIO16 |

| DIO19 | 21 | 22 | DIO18 |

| DIO21 | 23 | 24 | DIO20 |

| DIO23 | 25 | 26 | DIO22 |

| DIO25 | 27 | 28 | DIO24 |

| DIO27 | 29 | 30 | DIO26 |

| DIO29 | 31 | 32 | DIO28 |

| DIO31 | 33 | 34 | DIO30 |

| - | 35 | 36 | - |

| - | 37 | 38 | - |

| - | 39 | 40 | - |

NOTES:

Below is a chart of the 32 bit Digital I/O Port interconnections between the FMC connector's extra HPC columns, and the Altera Cyclone 5GX FPGA device:

| DIO Port, FMC & FPGA Connections | |||

| DIO Port Line | FMC Connector Pin | FPGA Bank & Pin | Direction |

| DIO_RDn | E15 | Bank 7A-C17 | FPGA->DIO |

| DIO_WR | E16 | Bank 7A-B17 | |

| DIO_DIR_HW | K16 | Bank 7A-H15 | |

| DIO31 | F17 | Bank 7A-E15 | BiDirectional |

| DIO30 | F16 | Bank 7A-F16 | |

| DIO29 | J16 | Bank 7A-C18 | |

| DIO28 | J15 | Bank 7A-C19 | |

| DIO27 | E13 | Bank 8A-G6 | |

| DIO26 | E12 | Bank 8A-F6 | |

| DIO25 | F14 | Bank 7A-D17 | |

| DIO24 | F13 | Bank 7A-D18 | |

| DIO23 | J13 | Bank 8A-L9 | |

| DIO22 | J12 | Bank 8A-M9 | |

| DIO21 | K14 | Bank 7A-F12 | |

| DIO20 | K13 | Bank 7A-G12 | |

| DIO19 | E10 | Bank 7A-B19 | |

| DIO18 | E9 | Bank 7A-C20 | |

| DIO17 | F11 | Bank 7A-C22 | |

| DIO16 | F10 | Bank 7A-C23 | |

| DIO_DIR_LW | K17 | Bank 7A-J16 | FPGA->DIO |

| DIO15 | J10 | Bank 5A-Y24 | BiDirectional |

| DIO14 | J9 | Bank 5A-Y23 | |

| DIO13 | K11 | Bank 7A-K11 | |

| DIO12 | K10 | Bank 7A-L12 | |

| DIO11 | E7 | Bank 5A-W21 | |

| DIO10 | E6 | Bank 5A-W20 | |

| DIO9 | F8 | Bank 7A-L11 | |

| DIO8 | F7 | Bank 7A-M11 | |

| DIO7 | J7 | Bank 5A-U20 | |

| DIO6 | J6 | Bank 5A-T19 | |

| DIO5 | K8 | Bank 5A-A23 | |

| DIO4 | K7 | Bank 5A-A22 | |

| DIO3 | E3 | Bank 8A-K6 | |

| DIO2 | E2 | Bank 8A-L7 | |

| DIO1 | F5 | Bank 5A-AB24 | |

| DIO0 | F4 | Bank 5A-AC24 | |

When the FMC connector is configured with the 200 contact Low Pin Count (LPC) option with only columns C-D-G-H defined, all analog I/O circuits and signals are supported. On the other hand, when the FMC connector on the carrier is configured with the 400 contact High Pin Count (HPC) option with all columns defined, the additional dual 16 bit port, 32 bit digital IO signals are also supported. Below is the connection diagram:

| FMC HPC Connector | ||||||||||

| Extra FMC HPC Columns | FMC LPC Columns | Extra FMC HPC Columns | FMC LPC Columns | Extra FMC HPC Columns | ||||||

| Row/Column Pin | K | J | H | G | F | E | D | C | B | A |

| 1 | VREF_B_M2C | GND | VREF_A_M2C | GND | PG_M2C | GND | PG_C2M | GND | - | GND |

| 2 | GND | - | PRSNT_M2C_L | - | GND | DIO2 | GND | - | GND | - |

| 3 | GND | - | GND | - | GND | DIO3 | GND | - | GND | - |

| 4 | - | GND | - | GND | DIO0 | GND | - | GND | - | GND |

| 5 | - | GND | - | GND | DIO1 | GND | - | GND | - | GND |

| 6 | GND | DIO6 | GND | - | GND | DIO10 | GND | - | GND | - |

| 7 | DIO4 | DIO7 | - | - | DIO8 | DIO11 | GND | - | GND | - |

| 8 | DIO5 | GND | - | GND | DIO9 | GND | - | GND | - | GND |

| 9 | GND | DIO14 | GND | - | GND | DIO18 | - | GND | - | GND |

| 10 | DIO12 | DIO15 | DAC_CLRn | - | DIO16 | DIO19 | GND | DAC1_SDO | GND | - |

| 11 | DIO13 | GND | DAC1_TGP | GND | DIO17 | GND | DAC1_LDACn | DAC1_SDI | GND | - |

| 12 | GND | DIO22 | GND | DAC0_LDACn | GND | DIO26 | DAC1_CSn | GND | - | GND |

| 13 | DIO20 | DIO23 | DAC1_SCLK | DAC0_CSn | DIO24 | DIO27 | GND | GND | - | GND |

| 14 | DIO21 | GND | DAC0_TGP | GND | DIO25 | GND | DAC0_SDO | DAC0_SCLK | GND | - |

| 15 | GND | DIO28 | GND | ADC0_SDOUT | GND | DIO_RDn | DAC0_SDI | - | GND | - |

| 16 | DIO_DIR_HW | DIO29 | ADC_SCLK | ADC0_CSn | DIO30 | DIO_WR | GND | GND | - | GND |

| 17 | DIO_DIR_LW | GND | ADC0_SDIN | GND | DIO31 | GND | ADC0_CNVRT | GND | - | GND |

| 18 | GND | - | GND | ADC1_BUSY | GND | - | ADC0_BUSY | ADC1_SDIN | GND | - |

| 19 | - | - | ADC1_CSn | ADC2_SDIN | - | - | GND | ADC1_SDOUT | GND | - |

| 20 | - | GND | ADC1_CNVRT | GND | - | GND | ADC2_SDOUT | GND | - | GND |

| 21 | GND | - | GND | ADC3_CSn | GND | - | ADC2_CSn | GND | - | GND |

| 22 | - | - | ADC3_SDIN | ADC3_CNVRT | - | - | GND | ADC2_CONVERT | GND | - |

| 23 | - | GND | ADC3_SDOUT | GND | - | GND | - | ADC2_BUSY | GND | - |

| 24 | GND | - | GND | ADC_RESET | GND | - | - | GND | - | GND |

| 25 | - | - | ADC3_BUSY | - | - | GND | GND | - | GND | |

| 26 | - | GND | - | GND | - | GND | - | - | GND | - |

| 27 | GND | - | GND | - | GND | - | - | - | GND | - |

| 28 | - | - | - | - | - | - | GND | GND | - | GND |

| 29 | - | GND | - | GND | - | GND | TCK | GND | - | GND |

| 30 | GND | - | GND | - | GND | - | TDI | SCL | GND | - |

| 31 | - | - | - | - | - | - | TDO | SDA | GND | - |

| 32 | - | GND | - | GND | - | GND | 3.3V AUX | GND | - | GND |

| 33 | GND | - | GND | - | GND | - | TMS | GND | - | GND |

| 34 | - | - | - | - | - | - | TRST_L | GA0 (msb) | GND | - |

| 35 | - | GND | - | GND | - | GND | GA1 (lsb) | 12V | GND | - |

| 36 | GND | - | GND | - | GND | - | 3.3V | GND | - | GND |

| 37 | - | - | - | - | - | - | GND | 12V | - | GND |

| 38 | - | GND | - | GND | - | GND | 3.3V | GND | GND | - |

| 39 | GND | VIO_B_M2C | GND | VADJ_A_C2M | GND | VADJ_A_C2M | GND | 3.3V | GND | - |

| 40 | VIO_B_M2C | GND | VADJ_A_C2M | GND | VADJ_A_C2M | GND | 3.3V | GND | - | GND |

NOTES:

| Power Consumption by Rails | |||||

| Circuit | Rail @ I = P | Efficiency | P on FMC +12Vdc Rail | P on FMC Vadj Rail (2.5V~3.3V) | Total P |

| ADC | FMC +12Vdc -> ±15Vdc @ 36mA = 540mW | 85% | 635mW | 7mW | 917mW |

| FMC +12Vdc -> +5Vdc @ 25mA = 125mW | 45% | 275mW | |||

| DAC | FMC +12Vdc -> ±15Vdc @ 92mA = 1380mW | 85% | 1625mW | 5mW | 1705mW |

| FMC +12Vdc -> +5Vdc @ 7mA = 35mW | 45% | 75mW | |||

| DIO | FMC +12Vdc-> +5Vdc @ 80mA = 400mW | 45% | 890mW | - | 890mW |

| SI-MOD32xx Power Consumption | ||||

| p/n | ADC Count x 8 Channels | DAC Count x 8 Channels | DIO Count | Power Total |

| SI-MOD3208 | 1 x 8 = 8 | ref. DAC count | ref. DIO option | 917mW |

| SI-MOD3216 | 2 x 8 = 16 | 1834mW | ||

| SI-MOD3232 | 4 x 8 = 32 | 3668mW | ||

| -8DAC Option | ref. ADC count | 1 x 8 = 8 | Add 1705mW | |

| -16DAC Option | 2 x 8 = 16 | Add 3410mW | ||

| -32DIO Option | ref. DAC count | x1 | Add 890mW | |